连云港碳化硅肖特基二极管多少钱一个

- 面议

- 2024-11-15 16:36:21

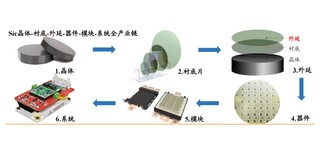

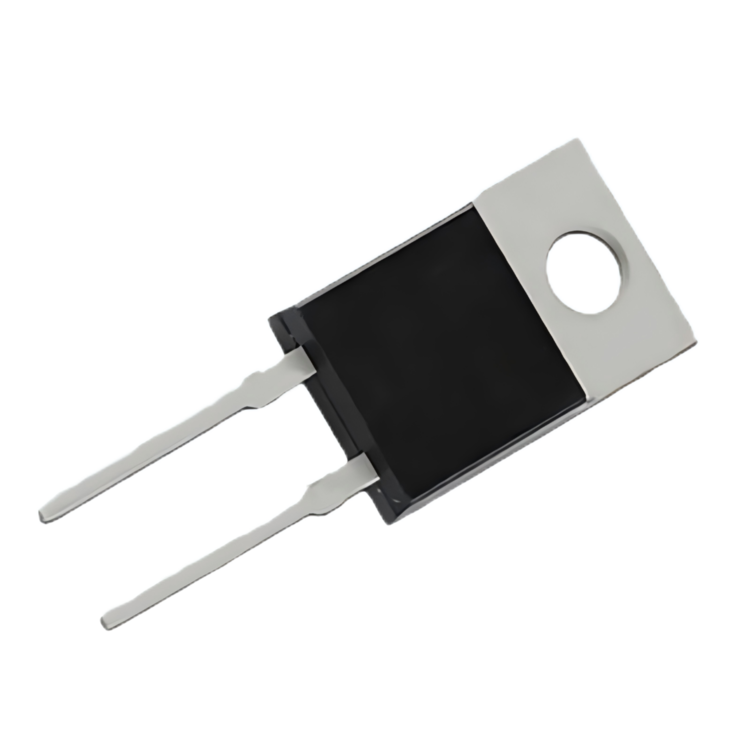

- 碳化硅肖特基二极管

- 叶友庆 18922939508

- 广东佳讯电子有限责任公司

信息介绍

详细参数

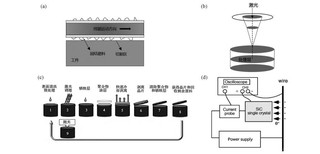

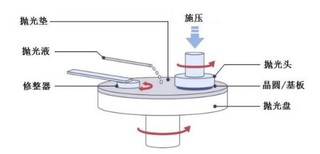

SiC MOSFET 的比导通电阻很低,工作频率很高,在高温下能够稳定的工作,它在功率器件领域很有应用前景。目前国际上报道的几种结构:UMOS、VDMOS、LDMOS、UMOS ACCUFET,以及 SIAFET 等。2008 年报道的双 RESURF 结构LDMOS,具有 1550 V 阻断电压.

SBD 在导通过程中没有额外载流子的注入和储存,因而反向恢复电流小,关断过程很快,开关损耗小。传统的硅肖特基二极管,由于所有金属与硅的功函数差都不很大,硅的肖特基势垒较低,硅 SBD 的反向漏电流偏大,阻断电压较低,只能用于一二百伏的低电压场合且不适合在 150 ℃以上工作。然而,碳化硅 SBD弥补了硅 SBD 的不足,许多金属,例如镍、金、钯、钛、钴等,都可以与碳化硅形成肖特基势垒高度 1 eV 以上的肖特基接触。据报道,Au/4H-SiC 接触的势垒高度可达到 1.73 eV,Ti/4H-SiC 接触的势垒比较低,但高也可以达到 1.1 eV。6H-SiC与各种金属接触之间的肖特基势垒高度变化比较宽,低只有 0.5 eV,高可达1.7 eV。于是,SBD 成为人们开发碳化硅电力电子器件关注的对象。它是高压快速与低功率损耗、耐高温相结合的理想器件。目前国际上相继研制成功水平较高的多种类的碳化硅器件。

肖特基二极管的反向阻断特性较差,是受肖特基势垒变低的影响。为了获得高击穿电压,漂移区的掺杂浓度很低,因此势垒形成并不求助于减小 PN 结之间的间距。调整肖特基间距获得与 PiN 击穿电压接近的 JBS,但是 JBS 的高温漏电流大于 PiN,这是来源于肖特基区。JBS 反向偏置时,PN 结形成的耗尽区将会向沟道区扩散和交叠,从而在沟道区形成一个势垒,使耗尽层随着反向偏压的增加向衬底扩展。这个耗尽层将肖特基界面屏蔽于高场之外,避免了肖特基势垒降低效应,使反向漏电流密度大幅度减小。此时 JBS 类似于 PiN 管。反向漏电流的组成主要由两部分:一是来自肖特基势垒的注入;二是耗尽层产生电流和扩散电流。

碳化硅具有载流子饱和速度高和热导率大的特点,应用开关频率可达到1MHz,在高频应用中优势明显,其中碳化硅肖特基二极管(SiC JBS)耐压可以达到6000V以上。相对应的,硅材料的禁带宽度较低,在较低的温度下硅器件本征载流子浓度较高,而高的漏电流会造成热击穿,这限制了器件在高温环境和大功率耗散条件下工作。

碳化硅肖特基二极管可广泛应用于开关电源、功率因素校正(PFC)电路、不间断电源(UPS)、光伏逆变器等中高功率领域,可显著的减少电路的损耗,提高电路的工作频率。在PFC电路中用碳化硅SBD取代原来的硅FRD,可使电路工作在300kHz以上,效率基本保持不变,而相比下使用硅FRD的电路在100kHz以上的效率急剧下降。随着工作频率的提高,电感等无源原件的体积相应下降,整个电路板的体积下降30%以上。

肖特基二极管是用于功率整流器应用的佳半导体器件,因为这些器件具有高电流密度和低正向电压降,与普通PN结器件的特性不同。这些优点有助于降低热量水平,减少设计中包含的散热器,并提高电子系统的整体效率。

- 碳化硅肖特基二极管

- 二极管

- 叶友庆