高精密电路板加工

- 面议

- 2024-12-26 05:02:45

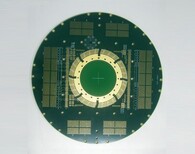

- VO板

- 常规板

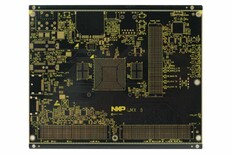

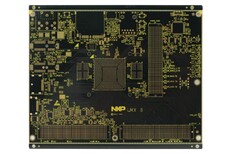

- PCB多层电路板

- 陈生 18938919530

- 深圳市赛孚电路科技有限公司

信息介绍

详细参数

PCB六层板的叠层

对于芯片密度较大、时钟频率较高的设计应考虑6层板的设计,推荐叠层方式:

1.SIG-GND-SIG-PWR-GND-SIG;对于这种方案,这种叠层方案可得到较好的信号完整性,信号层与接地层相邻,电源层和接地层配对,每个走线层的阻抗都可较好控制,且两个地层都是能良好的吸收磁力线。并且在电源、地层完整的情况下能为每个信号层都提供较好的回流路径。

2.GND-SIG-GND-PWR-SIG-GND;对于这种方案,该种方案只适用于器件密度不是很高的情况,这种叠层具有上面叠层的所有优点,并且这样顶层和底层的地平面比较完整,能作为一个较好的屏蔽层来使用。需要注意的是电源层要靠近非主元件面的那一层,因为底层的平面会更完整。因此,EMI性能要比种方案好。

小结:对于六层板的方案,电源层与地层之间的间距应尽量减小,以获得好的电源、地耦合。但62mil的板厚,层间距虽然得到减小,还是不容易把主电源与地层之间的间距控制得很小。对比种方案与第二种方案,第二种方案成本要**增加。因此,我们叠层时通常选择种方案。设计时,遵循20H规则和镜像层规则设计。

为什么要导入类载板

极细化线路叠加SIP封装需求,高密度仍是主线智能手机、平板电脑和可穿戴设备等电子产品向小型化和多功能化方向发展,要搭载的元器件数量**增多然而留给线路板的空间却越来越有限。在这样的背景下,PCB导线宽度、间距,微孔盘的直径和孔中心距离,以及导体层和绝缘层的厚度都在不断下降,从而使PCB得以在尺寸、重量和体积减轻的情况下,反而能容纳更多的元器件。

极细化线路要求比HDI更高的制程。高密度促使PCB不断细化线路,锡球(BGA)间距不断缩短。在几年前,0.6mm-0.8mm节距技术已用在了当时的手持设备上,这一代智能手机,由于元件I/O数量和产品小型化,PCB***使用了0.4mm节距技术。而这一趋势正向0.3mm发展,事实上业内对用于移动终端的0.3mm间距技术的开发工作早已开始。同时,微孔大小和连接盘直径已分别下降到75mm和200mm。行业的目标是在未来几年内将微孔和盘分别下降到50mm和150mm。0.3mm的间距设计规范要求线宽线距30/30µm,现行的HDI不符合要求,需要更高制程的类载板。类载板更契合SIP封装技术要求。

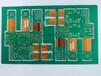

RF PCB的十条标准 之六

6.对于那些在PCB上实现那些在ADS、 HFSS等仿真工具里面仿真生成的RF微带电路,尤其是那些定向耦合器、滤波器(PA的窄带滤波器)、微带谐振腔(比如你在设计VCO)、阻抗匹配网络等 等,则一定要好好的与PCB厂沟通,使用厚度、介电常数等指标严格和仿真时所使用的指标一致的板材。比较好的解决办法是自己找微波PCB板材的代理商购买对 应的板材,然后委托PCB厂加工。

7.在RF电路中,我们往往会用到晶体振荡器作 为频标,这种晶振可能是TCXO、OCXO或者普通的晶振。对于这样的晶振电路一定要远离数字部分,而且使用的低噪音供电系统。而更重要的是晶振可能 随着环境温度的变化产生频率飘移,对于TCXO和OCXO而言,仍然会出现这样的情况,只是程度小了一些而已。尤其是那些贴片的小封装的晶振产品,对环境 温度非常敏感。对于这样的情况,我们可以在晶振电路上加金属盖(不要和晶振的封装直接接触),来降低环境温度的突然变化导致晶振的频率的漂移。当然这样会 导致体积和成本上的提升.

- PCB多层电路板

- 多层电路板

- 陈生

- VO板

- 常规板

- 多面

- 铜

- 有机树脂

- 环氧树脂(EP)