无锡善仁SiC碳化硅烧结银膏服务周到

1/6

- ¥1900.00

- 2024-12-27 03:41:15

- 金属类

- SiC碳化硅烧结银膏,宽禁带半导体烧结银,S..

- 刘志 13611616628

- 善仁(浙江)新材料科技有限公司

信息介绍

详细参数

善仁新材的纳米烧结银互连层的制作工艺

其工艺主要包括:

① 在覆铜(Cu)基板上涂覆或者丝网印刷纳米烧结银,将芯片放置在纳米银膏上;

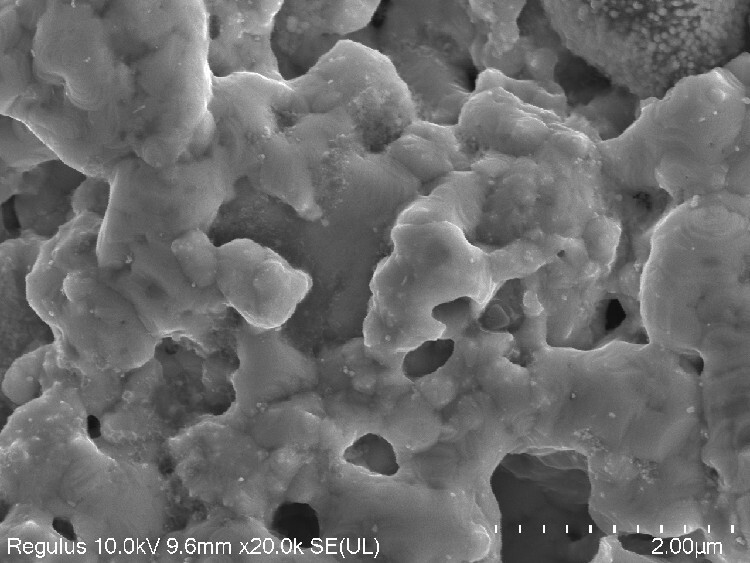

③烧结完成后形成SiC-Cu基板纳米烧结银互连层。可以看到,善仁新材的纳米银烧结互连层是碳化硅功率器件封装的关键结构单元,属于薄层结构,其厚度范围一般为20~50μm。SiC芯片和Cu基板表面可以通过镀银、金等烧结工艺提升其互连层的连接强度。

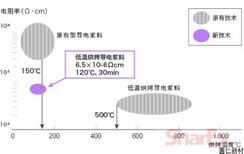

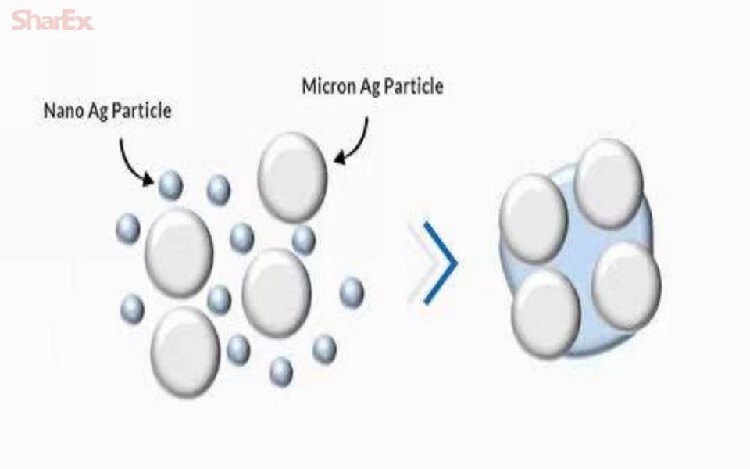

纳米烧结银互连层的工艺改进

善仁新材研究院比较了加压微米烧结银和无外加压力纳米烧结银,通过实验发现纳米尺度下的银具有比微米尺度下更高的烧结驱动力,避免了压力烧结条件下对芯片和基板中造成缺陷和裂纹等现象,并发现了烧结温度和烧结压强的增加会降低烧结银的孔隙大小,AS9375无压烧结银的纳米银互连层的结合强度可达45MPa。

另外,善仁新材研究院发现:较大面积的互连会导致较差的互连质量,其原因是增加的互连面积阻止了有机成分被燃尽,会导致更高的的孔隙率,针对这种现象,善仁新材提出了两个解决方案:

善仁新材研究院通过各种测试得知:纳米烧结银的互连层的空隙大小和空隙率高低和烧结温度,升温速率,保温时间等有密切的关系。

纳米烧结银互连层的蠕变性能

善仁研究院通过实验发现:蠕变应力指数以及激活能分别与环境温度和加载应力的关系很大,建议客户根据自己芯片的大小和界面的镀层材料选择适合的烧结温度和是否加压。

- SiC碳化硅烧结银膏,宽禁带半导体烧结银,S..

- 导电银胶

- 刘志

- 金属类

善仁(浙江)新材料科技有限公司为你提供的“无锡善仁SiC碳化硅烧结银膏服务周到”详细介绍