东莞SiC碳化硅烧结银膏性能可靠

1/6

- ¥1900.00

- 2024-10-04 03:51:23

- 金属类

- SiC碳化硅烧结银膏,宽禁带半导体烧结银,S..

- 刘志 13611616628

- 善仁(浙江)新材料科技有限公司

信息介绍

详细参数

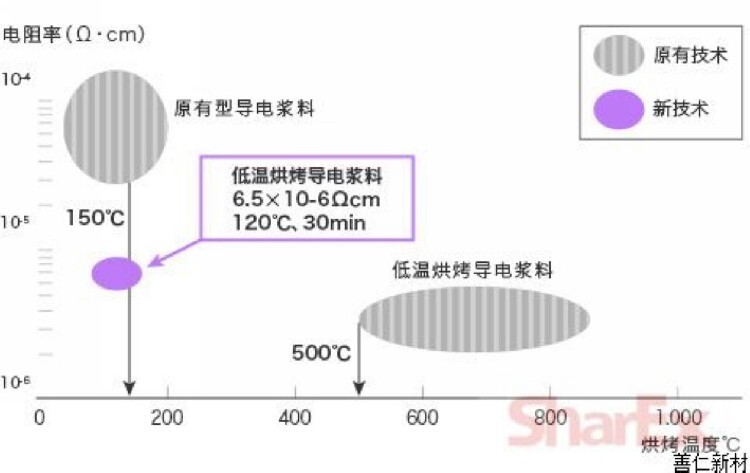

由于现有封装技术的限制,特别是芯片与基板的互连技术,例如银浆、聚合物材料,软钎焊等互连技术由于焊料合金的低熔点、环氧树脂的低温分解等原因,使其不能在高温环境下可靠工作,导致限制电力电子系统性能和可靠性的瓶颈从半导体芯片转移到了封装技术上来。

纳米烧结银互连层的孔隙研究

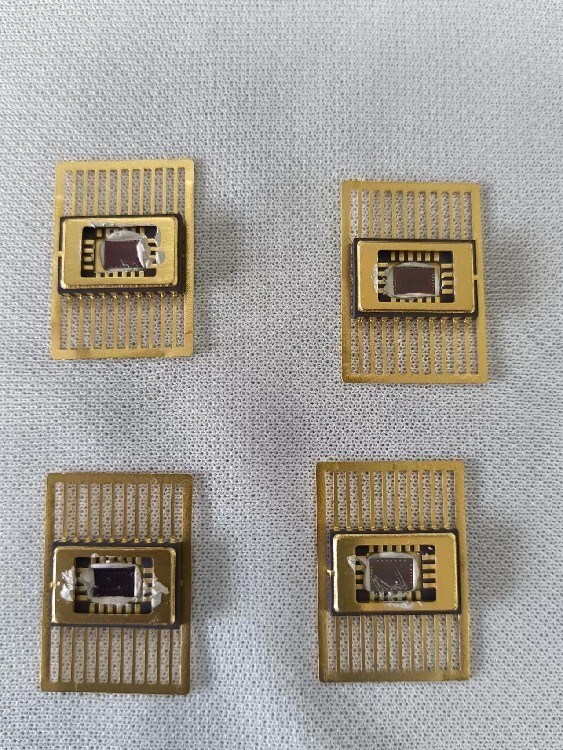

善仁公司统计了在不同时间和温度下孔隙率情况。发现孔隙率的大小和芯片的大小有很大的关系,采用无压纳米烧结银AS9375封装5*5mm的小芯片,几乎无孔隙。对于大于5*5mm的芯片,空隙率会在3-8%之间。孔隙主要由小孔和中孔组成,在250℃烧结时,空隙会很少。

总结和结论

本文通过对纳米烧结银互连层的形成原理、工艺、烧结后的微观形态及热、力学性能、蠕变本构等方面进行了简要综述。

- SiC碳化硅烧结银膏,宽禁带半导体烧结银,S..

- 导电银胶

- 刘志

- 金属类

善仁(浙江)新材料科技有限公司为你提供的“东莞SiC碳化硅烧结银膏性能可靠”详细介绍