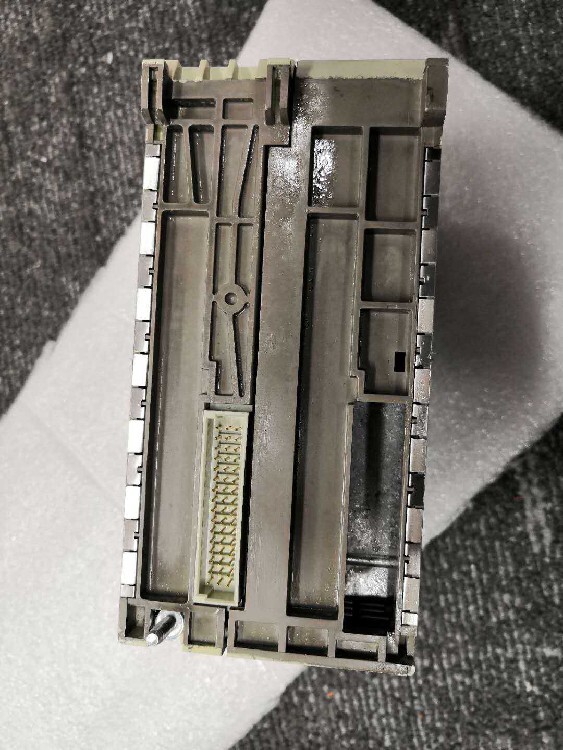

四川施耐德模块厂家电话,140CPU11303模块

- 面议

- 2024-12-22 17:30:39

- 施耐德模块,140CPU67160S控制器,TWDLCAA4..

- 四川绵阳

- 王经理 18005022138

- 深圳长欣自动化设备有限公司

信息介绍

详细参数

140DDI35300 内置多层缓存 CPU 从不直接访问 RAM。现代 CPU 有一层或多层缓存。CPU 执行计算的能力比 RAM 向 CPU 提供数据的能力要快得多。其原因超出了本文的范围,但我将在下一篇文章中进一步探讨。 高速缓存比系统 RAM 更快,并且更接近 CPU,因为它位于处理器芯片上。高速缓存提供数据存储和指令,以防止 CPU 等待从 RAM 中检索数据。当 CPU 需要数据时——程序指令也被认为是数据——缓存会判断数据是否已经驻留并将其提供给 CPU。 如果请求的数据不在缓存中,它会从 RAM 中检索并使用预测算法将更多数据从 RAM 移动到缓存中。缓存控制器分析请求的数据并尝试预测需要从 RAM 中获取哪些额外数据。它将预期的数据加载到缓存中。通过将一些数据保存在比 RAM 更快的高速缓存中更靠近 CPU,CPU 可以保持忙碌状态,而不会浪费等待数据的周期。 我们的简单 CPU 具有三级缓存。第 2 级和第 3 级旨在预测接下来需要哪些数据和程序指令,将数据从 RAM 中移出,并将其移至更靠近 CPU 的位置,以便在需要时准备就绪。这些缓存大小通常在 1 MB 到 32 MB 之间,具体取决于处理器的速度和预期用途。

假设计算机已收到从内存位置 10 读取数据的指令。为执行读取操作,140CPU65260该CPU 将 R/W 线提升到高电平以激活内存电路,为读取操作做准备。几乎同时,位置 10 的地址被放置在 AB 上。16位二进制(0000 0000 0000 1010)中的数字10被发送到AB中的内存中。10对应的二进制电信号操作内存中的特定电路,使该位置的二进制数据被放置到DB中。CPU 有一个内部寄存器,在读取操作期间被激活以接收和存储数据。然后CPU根据相关指令在下一个运行周期中处理数据。 每当 CPU 将数据从其内部寄存器之一发送到内存时,就会执行类似的操作,这是一种“写”操作。在这种情况下,R/W 线将设置为与读取操作相反的逻辑电平(即本例中的低电平)。写操作时,将要发送的数据放在DB中,同时目的地址放在AB中。此操作会将数据从 CPU 源位置传输到目标位置,目标位置可以是RAM中的内存位置,也可以是外部设备

为了让程序员设计出一个完整的程序,需要编写三个组件。 TSXCUSBMBP中央处理器代码: 通常用C 编程语言编写,CPU 代码通过调用由 Maxeler 编译器公开的适当函数来控制执行并使用 DFE 作为处理单元。 内核集: 每个内核都实现了一定的功能,大致相当于一个函数抽象。它有一组输入流和一组附加的输出流。

直流屏充电模块系统特点:

1、三相三线电压输入,三相电流平衡,具有交流过欠压保护功能;

2、宽电压输入范围304v~456v,适应能力强;

3、采用软开关技术,、电磁兼容性好,模块体积小、重量轻、模块性能高;

4、模块带电热插拔技术、维护方便快捷;

5、采用无级限流设计方式,电池充电限流精度高;

6、具有过压、限流、短路、并联、过温、过流等自动保护功能、告警措施;

7、模块有硬件均流单元电路,系统扩容变得简单;

8、采用智能温控风冷控制降温,具有噪音小,可靠性高。

IS200DSVOH1A是GE公司开发的伺服端子板。它是 GE Mark VI 涡轮机控制卡。几十年来,Mark VI 系统一直用于控制工业蒸汽和/或燃气轮机系统。 该板的目的是作为特定执行器或传感器的直接接口。典型的 Mark VI 系统中将使用多张卡。该组件是一个盒子中带有两个输入/输出通道的端子板。它有两个伺服电流源和六个 lvdt/lvdr 反馈传感器。 脉冲率输入范围为 2 至 14k Hz。PCB是一块又长又窄的矩形板。它的两个角有安装孔。在电路板的上部中心边缘附近,两个端子排并排放置。两个垂直母连接器位于下边缘。板上还有两个二位母插头。 其他电路板组件包括继电器、十几个跨接开关、晶体管、集成电路、电容器和电阻器。该板带有板 ID 号、代码 6BAO1 以及各种组件标识符。

IS200STCIH1A 是GE Mark VI 下的DIN RAIL 接触式输入卡。该系统是 GE 终推出的 Speedtronic 蒸汽或燃气轮机管理系统之一。Speedtronic 系列从 20 世纪 60 年代的 Mark I 开始,一直到 1990 年代的 Mark VI 和 Mark VIe,包含众多系统。

- 施耐德模块,140CPU67160S控制器,TWDLCAA4..

- 模块

- 四川绵阳

- 王经理

推荐信息

-

云南福克斯波罗模块多少钱P0916AA模块

云南福克斯波罗模块多少钱P0916AA模块 -

深圳DSQC604伺服系统配件厂家批发ASFC-01C模块

深圳DSQC604伺服系统配件厂家批发ASFC-01C模块 -

云南GE模块价格DS3820PSCB电机

云南GE模块价格DS3820PSCB电机 -

新疆西屋PLC系统生产厂家1C31116G04PLC系统

新疆西屋PLC系统生产厂家1C31116G04PLC系统