宿迁碳化硅肖特基二极管现货供应

- 面议

- 2025-01-18 18:15:26

- 碳化硅肖特基二极管

- 四川绵阳

- 叶友庆 18922939508

- 广东佳讯电子有限责任公司

信息介绍

详细参数

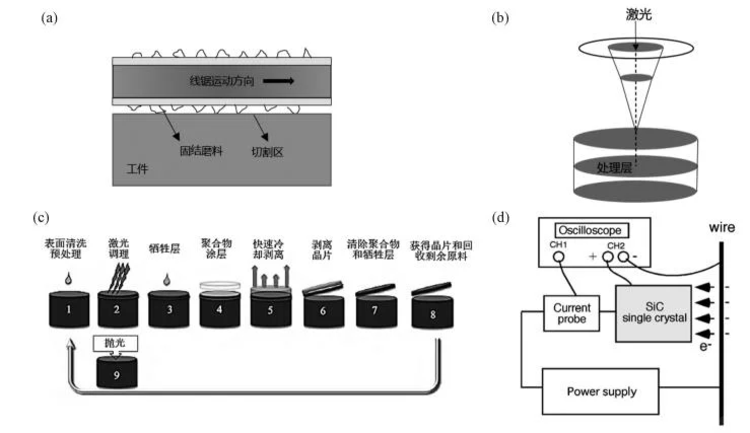

SiC MOSFET 的比导通电阻很低,工作频率很高,在高温下能够稳定的工作,它在功率器件领域很有应用前景。目前国际上报道的几种结构:UMOS、VDMOS、LDMOS、UMOS ACCUFET,以及 SIAFET 等。2008 年报道的双 RESURF 结构LDMOS,具有 1550 V 阻断电压.

国内的SiC功率器件研究方面因为受到 SiC 单晶材料和外延设备的限制起步比较晚,但是却紧紧跟踪国外碳化硅器件的发展形势。国家十分重视碳化硅材料及其器件的研究, 在国家的大力支持下经已经初步形成了研究 SiC 晶体生长、SiC器件设计和制造的队伍。电子科技大学致力于器件结构设计方面,在新结构、器件结终端和器件击穿机理方面做了很多的工作,并且提出宽禁带半导体器件优值理论和宽禁带半导体功率双极型晶体管特性理论。

功率二极管是功率半导体器件的重要组成部分,主要包括 PiN 二极管,肖特基势垒二极管和结势垒控制肖特基二极管。本章主要介绍了肖特基势垒的形成及其主要电流输运机理。并详细介绍了肖特基二极管和结势垒控制肖特基二极管的电学特性及其工作原理,为后两章对 4H-SiC JBS 器件电学特性的仿真研究奠定了理论基础。

金属与半导体的功函数不同,电荷越过金属/半导体界面迁移,产生界面电场,半导体表面的能带发生弯曲,从而形成肖特基势垒,这就是肖特基接触。金属与半导体接触形成的整流特性有两种形式,一种是金属与 N 型半导体接触,且 N 型半导体的功函数小于金属的功函数;另一种是金属与 P 型半导体接触,且 P 型半导体的功函数大于金属的功函数。

肖特基二极管的反向阻断特性较差,是受肖特基势垒变低的影响。为了获得高击穿电压,漂移区的掺杂浓度很低,因此势垒形成并不求助于减小 PN 结之间的间距。调整肖特基间距获得与 PiN 击穿电压接近的 JBS,但是 JBS 的高温漏电流大于 PiN,这是来源于肖特基区。JBS 反向偏置时,PN 结形成的耗尽区将会向沟道区扩散和交叠,从而在沟道区形成一个势垒,使耗尽层随着反向偏压的增加向衬底扩展。这个耗尽层将肖特基界面屏蔽于高场之外,避免了肖特基势垒降低效应,使反向漏电流密度大幅度减小。此时 JBS 类似于 PiN 管。反向漏电流的组成主要由两部分:一是来自肖特基势垒的注入;二是耗尽层产生电流和扩散电流。

碳化硅肖特基二极管的开启导通电压比硅快速恢复二极管较低,如果要降低VF值,需要减薄肖特基势垒的高度,但这会使器件反向偏压时的漏电流增大。碳化硅肖特基二极管的温度特性与硅快速恢复二极管不同,当温度升高时导通阻抗会增加,VF值也上升,这样器件发热不易发生热失控,更适合并联使用。

- 碳化硅肖特基二极管

- 二极管

- 四川绵阳

- 叶友庆